IBM’s Server Processors: The RS64 and the POWER

IBM in the late 1990s was making a wide variety of processors, from the Cyrix Design 6x86MX, to fab work for AMD on the K6, to the PowerPC line used in Apple computers. Most of these processors were low margin designs for the consumer market. What IBM is best known for, and best at, is server and workstation processors. The kind of processors you will find by the thousands in Top 500 Supercomputers.

There were three distinct architectures IBM used in this market. The POWER (Performance Optimization With Enhanced RISC) processor originated in 1990 as a new deign for IBM. IBM also was working on with Apple and Motorola in a consortium known as AIM to design a PC based processor architecture, loosely based, or inspired by, POWER. This became known as the PowerPC. IBM also was looking for a solution to replacing their old AS/400 CISC based computers. A processor architecture to smooth the transition from CISC, to full on RISC was needed. A subset of the PowerPC design was developed with added instructions from the POWER2 and AS/400 called PowerPC-AS. The first CPU to use this architecture was the A10, released in 1995 at 77MHz

The RS64 line implemented the PowerPC-AS architecture and was initially released in 1997. RS64 designs were focused mainly on transaction processing and other integer intensive applications. Their floating point performance was not as good as the POWER architecture. Debuting at 125MHz with 128kb of L1 cache, and 4MB of off chip L2 cache. By 2000 IBM had continually improved upon the RS64 architecture, as well as fab processes. The RS64-IV, the final RS64 processor, was released at 600MHz and topped out at 750MHz. At the time the POWER line (now at the POWER3) has stagnated, the RS was able to clock twice as fast, and at less power (15W per core)

In 1998 IBM released the POWER3, the third generation in the POWER line, and the contemporary to the RS64-IV. The POWER3 essentially merged the full 64-bit PowerPC instruction set into the POWER line. Initially it ran at 200MHz with 96kb of L1 cache, 16MB of off chip L2 cache. It was manufactured on a hybrid 0.35/0.25u process. In 2000 IBM released the POWER3-II, a process shrink to 0.22u, with other enhancements, that brought the POWER line up to 450MHz. Still the POWER3 languished in pure speed (at least in integer) against the RS64-IV.

Having two independent processor lines is extremely expensive to maintain. Support costs, software costs, R&D, etc all were double what they would be with a single unified architecture. In 2001 IBM released the POWER4 and discontinued the RS64 line. The POWER4 merged the PowerPC (and POWER) instruction sets with the PowerPC-AS instruction set of the RS64.

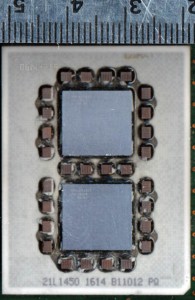

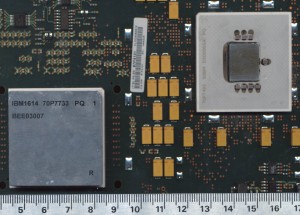

Now IBM had a single processor for both the RS/6000 line and the AS/400 line of computers. The POWER4 was also an incredible boost in speed and now featured 2-cores on one die (the first non-embedded processor to do so). Even the initial version did 1.1GHz. L2 cache size was decreased to 1.4MB but moved on die. L1 cache remained at 96kb. To compensate for the reduced L2 cache size IBM added a 32mb off chip L3 cache. The POWER4+ would eventually hit 1.9GHz. In the picture on the left the 32MB of L3 cache is the large white chip in the upper right, while the dual core CPU is in the lower left.

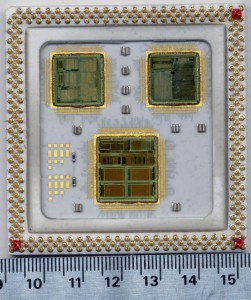

In 2003 IBM further enhanced the POWER line and released the POWER5 processor. Again a dual core processor running at 1.5-2.3GHz. The POWER5 increased the on chip L2 cache to 1.9MB and moved the L3 cache on chip (though a separate die, like the Pentium Pro). The L3 cache was also increased to 36mb. As with the POWER4 the POWER5 was also offered in larger MCMs that integrated 4 processor dies, and 4 36mb L3 cache dies onto a single, large, MCM. IBM has an excellent, in depth article on the differences of the POWER4 and POWER5 here. IBM continues to develop the POWER line and currently is shipping system based on the 4GHz+ POWER7 processor. The POWER8 successor is under development.

Posted in:

CPU of the Day