Cyrix Joshua Processor – From Peppers to the Bible

Perhaps one of the most confusing, and misreported processor stories is that of the Cyrix Joshua processor. More correctly known as the VIA Cyrix III Joshua. Cyrix began sampling this successor to the MII in 1999, a tumultuous time in Cyrix’s history, as they were in the midst of being sold to VIA by National Semiconductor. The Joshua never made it into full production, being quickly killed off by the Centaur designed Samuel core. Centaur was the processor division of IDT which produced the Winchip series, bought by VIA only a month after their purchase of Cyrix.

Adding to the confusion was Cyrix bountiful use of code names for its upcoming products, with many seeming to overlap, change or be redundant. Understanding the methodology of their naming will greatly increase ones understanding of the products. Cyrix used a code name for the core of a processor, as well as a separate name for what application that core was going to be used in. Just like Intel used the P6 core for the PII, Celeron, and Xeon, Cyrix intended its cores to be able to be used in several products.

In the late 1990’s Cyrix had two new cores under development. The first was the Cayenne, an evolution of the 6x86MX/MII processor. The Cayenne was essentially an MII, with a dual (rather then single) issue FPU, support for 3DNow! instructions, and perhaps most importantly, a 256K 8-way associative on-die L2 cache. It retained the 7 stage pipeline of the MII, the 256 byte scratch pad L0 cache, an almost identical X-Y integer unit and the same 64K L1 cache. Cyrix had had industry leading integer performance, but always lagged in the area of FPU performance. The dual issue FPU was their attempt to help remedy this. However, FPU intensive benchmarks, such as Quake 3, showed the Cayenne core to be about half as fast as a Celeron of equal rating (500MHz vs PR500 Cyrix). Business apps, heavy in integer and light on floating point, showed the integer strength of the Cyrix, with a 400MHz Cyrix matching a 500MHz Celeron.

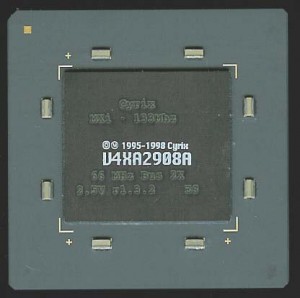

The Cayenne core was slated to be used in at least 3 different products. The first was the MXi, this was the successor to the MediaGX and thus would be highly integrated, including a PCI Bus controller, SDRAM controller, MPEG/DVD acceleration, 2D/3D Graphics as well as audio capabilities. The Jedi was to be a socket 7 (Super 7 really) compatible processor based on the Cayenne core. This was canceled in 1999 (nothing to do with potential lawsuits from Lucas Films as often was rumored). The third use of the Cayenne core was the Gobi, this was to be a Socket 370 compatible processor and it is this version that was widely sampled, and benchmarked, by many hardware review sites, magazines, etc. When VIA purchased Cyrix on June 30, 1999 the Gobi project was allowed to continue, MXi, and other projects were quickly shut down. The Gobi codename did not fit with VIAs core naming scheme however, thus is was renamed.

Thus the Cyrix III Joshua (a leader of Israel in the Old Testament, and keeping in line with VIA’s Wen Chi Chen’s Christian code names) was born. The Joshua, with its 7-stage Cayenne core was expected to top out at around 600MHz. VIA planned on replacing it then with the Samuel core, which, developed by the recently purchased Centaur team, had 12 stages and thus could be easily clocked higher. Unfortunately the thermal, and power envelope of the Joshua did not meet VIA’s needs for it. At 450 MHz Joshua was consuming close to 25 Watts, while the Samuel core drew closer to 6 Watts at similar clocks. This led VIA to cancel the Joshua project, and use the Centaur C5 Samuel core for the Cyrix III processor line.

This story is not complete without covering the other Cyrix core under development at the time of the VIA purchase. This was the Jalapeno core. The Jalapeno was a complete new core, dual issue FPU, register renaming, and out-of-order execution all were supported. It was based on an 11 stage pipeline and was expected to be clocked in the 600-800MHz range. The Jalapeno core was to be used in the Mojave S370 processor and include integrated 3-D graphics which could store textures in the processors 256K of on die L2 cache. The Jalapeno core was also to have a RAMBUS ASIC cell memory controller on die, the first processor to have an on die RAMBUS controller, had it been produced. Various references and articles give somewhat conflicting reports on the amount of L1 cache. Most references claim 16K while others claim 16K instruction and 16K Data for a total of 32K. Being as the Jalapeno was never fully taped out, it is possible that a firm decision had not yet been made. The Mojave team was let go in the massive layoffs immediately after VIA purchased Cyrix from National Semiconductor. It is doubt any samples were ever made as no evidence exists to suggest the Jalapeno core was even taped out (laid out for masks to be made, leading to actual physical chips).

Below is a chart detailing the differences in the Cyrix/VIA processor core at the time of the transition (1999-2000)

| Processor | MII (6x86MX) | Joshua – Gobi – Jedi(Cayenne Core) | Mojave(Jalapeno Core) | VIA C3 (Samuel – Centaur C5A) |

| Socket | Socket 7 | Jedi– S7 Joshua/Gobi -S370 |

S370 | S370 |

| Supply Voltage | 2.2-2.9V** | 2.2V | 1.8V?^ | 1.9-2.0V |

| L1 Cache | 64K 4-way | 64K 4-way | 16K or 32K 4-Way^ | 128K 4-Way |

| L2 Cache | external | 256K 8-way | 256K 8-way | 0K |

| MMX | Yes | Yes | Yes | Yes |

| 3D Now! | No | Yes | Yes | Yes |

| Integer Units | 2 | 2 | 2 | 1 |

| FPU Units | 1 | 2 | 2 | 1 |

| Pipeline Stages | 7 | 7 | 11 | 12 |

| Process | 0.35u-0.18u** | 0.18u | 0.18u | 0.18u |

| Speeds (MHz) | 150-300 | 333-450 | 600+ | 400-800 |

| Power (W) | 17.6-27.9 (2.9V)8.8-13.7 (2.2V) | 20.1-24.6 | ?? | 5.6-19.3 |

| Transistors | 6.5 Million | 22 Million | 25 Million | 11.3 Million |

**Late National Semiconductor production parts scaled to 300MHz at 0.18u and used much less power then early 0.35 and 0.25u parts

^There are conflicting reports as to the voltage and L1 cache, most likely since this processor never made it off paper.

Sources:

EE Times: Cyrix Serves Jalapeno Core

FiringSquad: Cyrix III Joshua Launch

Cyrix III Joshua Datasheet (VIA)

National Semiconductor Press Release: Jalapeno unveiled

Forbes: Taiwan Inc. Ready to snap up Cyrix?

The Real VIA/Cyrix Layoff Story

ARS Technica: Joshua