nCube and the Rise of the HyperCubes

In 1983 Stephen Colley, Dave Jurasek, John Palmer and 3 others from Intel’s Systems Group left Intel, frustrated by Intel’s seeming reluctance to enter the then emerging parallel computing market. They founded a company in Beaverton, Oregon known as nCube with the goal of producing MIMD (Multiple Instruction Multiple Data) parallel computers. In 1985 they released their first computer, known as the nCube/10. The nCube/10 was built using a custom 32-bit CMOS processor containing 160,000 transistors and running initially at 8MHz (later increased to 10). IEEE754 64-bit floating point support (including hardware sqrt) was included on chip. Each processor was on a module with its own 128KB of ECC DRAM memory (implemented as 6 64k x 4 bit DRAMs.) A full system, with 1024 processor nodes, had 128MB of usable memory (160MB of DRAM counting those used for ECC). From the outset the nCube systems were designed for reliability, with MTBFs of full systems running in the 6 month range, extremely good at the time.

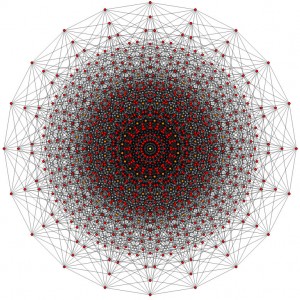

The nCube/10 system was organized in a Hypercube geometry, with the 10 signifying its ability to scale to a 10-way Hypercube, also known as a dekeract. This architecture allows for any processor to be a maximum of 10-hops from any other processor. The benefits are greatly reduced latency in cross processor communication. The downside is that expansion is restricted to powers of 2 (64, 128, 256, 512 etc) making upgrade costs a bit expensive as the size scaled up. Each processor contained 22 DMA channels, with a pair being reserved for I/O to the host processor and the remaining 20 (10 in + 10 out) used for interprocessor communication. This focus on a general purpose CPU with built in networking support is very similar to the Inmos Transputer, which at the time, was making similar inroads in the European market. System management was run by similar nCube processors on Graphics, Disk, and I/O cards. Programming was via Fortran 77 and later C/C++. At the time it was one of the fastest computers on the planet, even challenging the almighty Cray. And it was about to get faster.

Interestingly Intel seemed to have gotten the message, for in 1985 they released the iPSC, a 16-128 node 286/287 based parallel hypercube system. Later Intel upgraded this to the iPSC/2 which used 386/387 processors and finally a version with the 64 bit i860 RISC processor.

In 1989 nCube released a new version of their processor. The nCube/2 was a greatly enhanced processor. Transistor count was now on the order of 500,000 manufactured on a CMOS bi-metal 1 micron process. Clock speeds were 20MHz initially and scaled to 25MHz and 30MHz in later versions. The integer unit was now a full 64-bits and an on-chip MMU was now included along with the DRAM controller and networking support. On chip Instruction and Data caches were also included, but very small to make room for the networking logic (500k transistors was pushing the limits of most 1 micron processes). The instruction cache was 128 bytes and the Data cache was 64 bytes (8 64-bit operands). Networking channels were increased from 22 of the nCube/10 to 28. Two remained for bi-directional I/O while the remaining 26 formed 13 pairs for inter-processor communication. This of course now allowed for a 13-way Hypercube arrangement, supporting a maximum of 8,192 nodes in a system. nCube used such a system called the Series Scalar Supercomputer in 1989 to set records for processing power. A maxed out system supported 512GB of RAM (64MB per node) and 16 Terabytes of disk. Remember this was 1989 when a PC had 4MB of RAM and a 100MB hard drive. A 64 node ‘basic’ system cost around $250,000. Unlike the nCube/10 the nCube/2 now used a Sun workstation to program and manage it. Essentially the nCube system worked as a co-processor being assigned tasks by the host computer and reporting the results when done. Very similar to how a math-co-processor worked at the time, or how most supercomputers continue to work today.

In 1990 Larry Ellison (of Oracle fame) invested heavily in nCube and nCube moved to Foster City, CA to be closer to Oracle. Their focus began to shift to database processing and Video On Demand technology. In 1995 the nCube/3 was released, an enhanced nCube/2 with larger caches, faster networking and support for 65,536 (16-way hypercube) nodes. The nCube/3 was the last of the custom nCubes. The later versions (4 and 5) used Intel IA32 Xeon processors, similar to many supercomputers today. In 1996 Larry Ellison took over as CEO with the goal of making nCube the networking division of Oracle. In 2006 nCube was sold to C-COR, which was then bought by ARRIS (makers of cable modems and other cable equipment), thus bringing the end to nCube.

At one time nCube commanded almost 10% of the MIMD supercomputer market. A market that at the time was controlled by Thinking Machines and eventually Intel. In the 1980’s there was the Cray X-MP and Y-MP, vector based (SIMD) super computers, and then there was ‘everyone else.’ Cray dis-regraded MIMD supercomputing as ‘hard to program’ and insisted that vector was the best solution. In 1993 Crazy released the T3 series of MIMD supercomputers, and by 2000 NEC and Cray were the only 2 companies left making vector based computers. nCube, the Hypercube, and massively parallel super computing had won, even if by then nCube was merely a footnote.

Sources:

- Parallel Computing: Principles and Practice – T. J. Fountain – 2006 – pg 247-256

- Hypercube: Multiprocessors, 1987: Proceedings on the 2dn Conference on Hypercube Multiprocessors – Michael T. Heath – Jul 1987 – pg 384-386

- Parallel Computer Architecture: A Hardware/Software Approach – David E. Culler et al – 1998 – pg 463-464

- Hypercube Multiprocessors – Michael T. Heath – 1986 – pg 19-26

- Popular Science – Speed Barriers – September 1989 pg 21

- Computerworld – THinking Machine Thinks Big – Michael Alexander – Nov 4 1991 pg 12

April 8th, 2016 at 1:29 am

That was a really interesting read.

September 5th, 2016 at 4:57 pm

Was this the first Hypercube computer or was CalTech?

September 13th, 2016 at 1:09 am

Neither actually. M. C. Pease proposed a binary n-cube architecture for several numerical algorithms

including the fast Fourier transform; and in 1975, IMS Associates (IMSAI) announced The Hypercube, a 4-dimensional computer based on his ideas.The Hypercube had thirty-two 8-bit microprocessors (Intel 8080As) arranged in a 4-cube with two processors at each node, one for computation and one to handle internode communication. The machine was not commercially successful because its architecture was too advanced for the microprocessor technology available to implement it. This predated CalTechs Cosmic Cube, though CalTech did a lot of work in defining how the communication of a HyperCube worked.

July 4th, 2017 at 8:50 am

[…] computing hyprecube […]

December 12th, 2017 at 7:53 am

I am an old friend and college roommate of Stephen Colley. I have been looking for him for a while now but the last address I have for him, in Morgan Hill, doesn’t seem to be his anymore. My name is Henry Laxen. I would really like to reconnect with him. If you have any idea where he is these days, please let me know.

July 29th, 2019 at 4:34 pm

i am am almost sure i there was ncube 64 ncube at u of m that was difficult.