DEC Rigel: VAX Shoots for the Stars

DEC’s 32-bit VAX architecture saw many implementations since its introduction in 1977. Early implementations were all multi-chip, but as technology improved the VAX architecture could be implemented (at least partially) on a single VLSI chip. The first implementation on a single chip was the MicroVAX II released in 1985. It contained 125,000 transistors, made on a 3 micron NMOS (DEC proprietary ‘ZMOS’) process and ran at 5MHz (200ns cycle time).

In 1987 DEC released the CVAX, the second generation VAX on VLSI. The CVAX was made on DEC’s first CMOS process, a 2 micron design using 175,000 transistors and clocked from 10-12.5 MHz (80-10ns cycle time). The input clock was a four-phase overlapping clock (so input frequency was 4x the cycle time, or 40-50MHz). Performance was 2.5-3 times better then the MicroVAX II. About half the gain was from process improvement (increased clock speed), while the rest was from architectural changes (mainly pipelining).

As the CVAX (and its successor the CVAX+) were released the next generation was already being designed by DEC. This was to be Rigel. Rigel has a 6-stage pipeline, and was made on a 2 micron CMOS process and the CPU contained 320,000 transistors, 140k of which were for logic, while the remaining 180k were for memory (cache). The separate FPU chip contained an additional 135,000 transistors. After some early teething pains on the new CMOS process, where yields were almost non-existent, the process finally was refined enough to make commercial samples by late 1988. The target speed for Rigel was a 40ns cycle (25 MHz clock). This would give the Rigel a 6-8x performance gain over CVAX. 2X of this was from the process shrink (and doubling of clock speed) while 3X was from the improved pipelining. The remainder was due to increased memory performance, not the least of which was due to Rigels 2KB of on chip cache.

Rigel, however, had other plans…

Rigel outperformed, and did so by a fair amount. Most parts clocked well at 35MHz with some hitting 40MHz and a select few able to be pushed to over 50MHz. This is nearly double the performance expected and quickly placed Rigel ahead of even DEC’s, at the time, high end VAX systems.

Like the CVAX the Rigel required a four-phase overlapping clock. This is why you see a 143MHz crystal on the KA670 board, and why much of the DEC documentation refers to the Rigel as a 143MHz processor. The primary clock generator (DC521) divides and shifts the 143MHz clock into four 35.75MHz phases, which give the 28ns cycle time of the Rigel. For 1989, when Rigel systems were sold, 35-40MHz was incredibly fast.

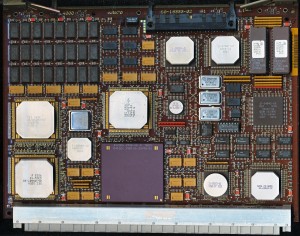

The KA670 board pictured contains the following ICs:

DC520 (P-chip): VAX. central processor -21-25087-10

DC523 (F -chip): Floating point accelerator -21-25090-02

DC592 (C-chip): L2 cache controller (220,000 transistors) + bank of associated RAM chips (128KB total) -21-29572-04

DC561 (G-chip): Main memory controller (later revision called the DC250A) 21-33498-01

DC521: Clock Driver (divides 143MHz clock to four phases) – 21-25088-02

DC527 (CQBIC): Q22-bus interface – 21-25972-02

DC541 (SGEC): Ethernet interface – 21-28059-01

DC542 (SHAC): DSSI interface chips (2) – 2127667-01

DC511 (SSC): System support chip – 21-24942-03

In 1991 the last of the VAX line was released with the introduction of the NVAX. DEC continued to make the MicroVAX II, CVAX+ and Rigel well into the 90’s until they were slowly replaced by the DEC Alpha.