MHTL: Before the Processor

Before the single chip processor, the Intel 4004, TI TMS1000, or Four Phase AL-1 (depending on your school of thought) ‘processing’ was done by discrete logic. These are SSI IC’s (Small Scale Integration), a step up from literal discrete transistors, each IC contains 2-30 transistors, implementing a couple gates.

The most famous of these is the TTL (Transistor-Transistor Logic) series developed by Sylvania in 1963. Before TTL though their was RTL (Resistor-Transistor Logic) in 1961 and the next year, DTL (Diode-Transistor Logic), whereby Diodes were added to the inputs, allowing much better fan-in. Neither of these designs had great noise immunity, which in many applications was very important. Motorola patented a modification to DTL in 1966 with production of the new MHTL family commencing in 1967-1968.

MHTL, Motorola High Threshold Logic, was designed for environments where high noise immunity was a must. Noise, really any voltage that is present, and not wanted/not an actual signal, can be complicated to deal with. Motorola’s solution was to make the signal much larger, this s clearly the ‘bigger hammer’ approach to noise. Normal DTL has a turn on voltage of 1.5V (0-5V Logic). fairly low, and in an industrial environment, where these IC’s may be controlling large motors and solenoids, a common noise voltage. MHTL raised that to 7.5V, requiring a 15V supply. Speed suffers greatly, as the voltage must now swing from 0-15V for a logic 0 to a logic 1 on the outputs, 3MHz being a typical max compared to 40MHz for Motorola’s DTL. It should be noted, that as fast as that sounds, it’s only for a few gates, a full board of these will not be able to attain anything close to 3MHz due to propagation delays through the many IC’s.

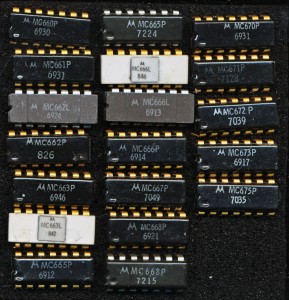

The pictured MHTL devices are:

| Device | Function | Transistors | Power (mW) |

| MC660 | Exp 4 Input NAND (Passive Pullup) | 6 | 88 |

| MC661 | Exp 4 Input NAND (Active Pullupt) | 4 | 88 |

| MC662 | Expandable 4-Input NAND Line Driver | 6 | 180 |

| MC663 | Dual J-K Flipflop | 24 | 200 |

| MC665 | Triple Level Translator (for interface to DTL, RTL or TTL) | ?? | 104 |

| MC666 | Triple Level Translator | ?? | 105 |

| MC667 | Dual monostable multi vibrator | ?? | 240 |

| MC668 | Quad 2-Input NAND Gate (Passive pullup) | 8 | 176 |

| MC670 | Triple 3-Input NAND Gate (Passive pullup) | 6 | 132 |

| MC671 | Triple 3-Input NAND Gate (Active pullup) | 9 | 132 |

| MC672 | Quad 2-Input NAND Gate (Active pullup) | 12 | 176 |

| MC673 | Dual 2-Input AND-OR-INVERT (Active pullup) | ?? | 160 |

| MC675 | Dual Pulse Stretcher/Multivibrator | ?? | 180 |

Today, noise immunity is still relevant, and much much more complex than simply increasing the supply voltage. Higher supply voltages not only slow down switching, but they also increase power draw significantly. The MC660 pictured has exactly 2 gates (4-input NAND), consisting of 6 transistors, and still dissipates 88mW. That would be the equivalent of an Intel 4004 dissipating 12 Watts, or an Intel 386 needing about 4 Kilowatts. Modern noise immunity is handled by adding additional transistors (keepers, pre-chargers, etc) that can keep gates from being affected by noise, whether it’s from power/ground lines, leakages, or other reasons. This allows chips with millions of transistors to operate at sub 1 Volt levels. An impressive feat.

Posted in:

CPU of the Day