Intel i486 Prototype: Intel’s Gamble with CISC

The Intel 80486 was announced at COMDEX in April 11th 1989, justy 3 years after the 80386 hit the market. The 80486 was really a greatly enhanced 80386. It added a few instructions, on-chip 8KB Write-Thru cache (available off chip on 386 systems) as well as an integrated FPU. Instruction performance was increased through a tight pipeline, allowing it to be about twice as fast as the 80386 clock for clock. Like the 80386 the 80486 was a CISC design, in an era when the RISC processor, in its may flavors, was being touted as the future of ALL computing. MIPS, SPARC, and ARM all were introduced in the late 1980’s. Intel themselves had just announced a RISC processor, the i860, and Motorola had the 88k series. Intel in fact was a bit divided, with RISC and CISC teams working on different floors of the same building, competing for the best engineering talent. Would the future be CISC, with the 80486? Or would RISC truly displace the CISC based x86 and its 10 years of legacy?

This dilemma is likely why Intel’s CEO, Andy Grove, was nearly silent at COMDEX. It was only 4 years previous the Mr. Grove, then as President, made the decision to exit the memory market, and focus on processors, and now, a decision would soon loom as to which type of processor Intel would focus on. Intel eventually ditched the i860 and RISC with it, focusing on the x86 architecture. It turns out that ultimately CISC vs RISC didn’t greatly matter, studies have shown that the microarchitecture, rather then the Instruction Set Architecture, is much more important.

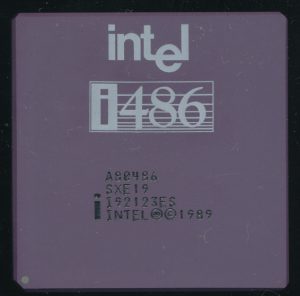

Whether due to the competition from the i860 RISC team, or knowing the markets demands, the 80486 team knew that the processor had to be executed flawlessly. They could ill afford delays and bugs. Samples of the 80486 were scheduled to be released in the 3rd quarter of 1989 with production parts shipping in the 4th quarter. The above pictured sample is from May of 1989, a quarter ahead of schedule. Production parts began to ship in late September and early October, just barely beating the announced ship date.

Perhaps due to the rush to get chips shipping a few minor bugs were found in the FPU of the 486 (similar to bugs found in the FPU of the 387DX). Chips with the B4-Mask revision and earlier were affected (SX249). These bugs were relatively minor and quickly fixed in the B5 mask revision (SX250), which became available in late November of 1989, still within Intel’s goal of the 4th Quarter.

The 80486 was a success in the market and secured CISC as the backbone of personal computing. Today, the CISC x86 ISA is still used, alongside the greats of RISC as well.

Tags:

80486.CISC.RISC, Intel

Posted in:

CPU of the Day