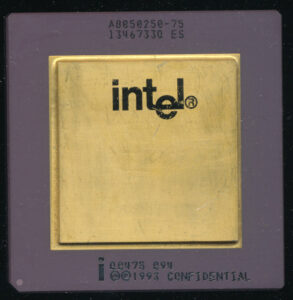

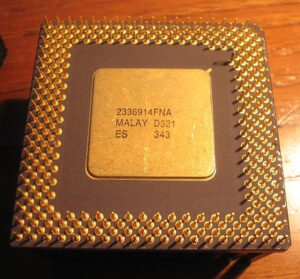

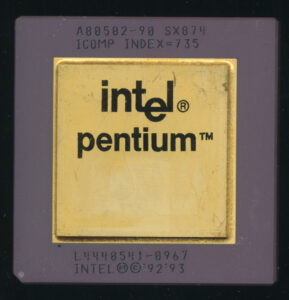

Intel Pentium P54CM – Q0475 Engineering Sample from November 1993

Today dual processors are incredibly common, even in home computing, and multicore processors even more common, but there was a time when this was not so. There were of course multi-processor systems in the 80’s and early 90’s, but these required extensive additional hardware to support them. Three main concerns for design multiprocessing systems are how to efficiently handle interrupts (which CPU handles what), how to ensure the caches are kept current (and not used if they aren’t), and how do processors share the same bus.

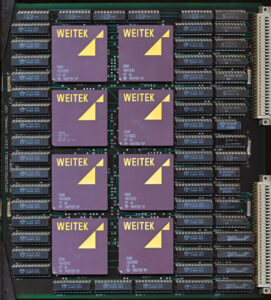

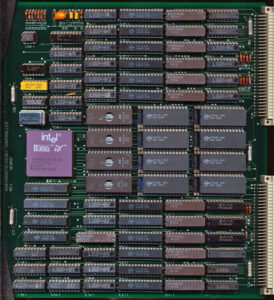

Bus sharing was largely handled already as busses have long been shared by all sorts of devices. Interrupts were made easier by the release of the APIC (Advanced Programmable Interrupt Controller) standard by Intel in the early 1990’s.. The first version of this was implementing in the 82489DX IC. Each CPU (486 or original P60/66) would need its own 82489DX (Local APIC) and then yet another one to work as an I/O APIC. Clunky, but it worked. The BIOS and OS were designed to help with cache coherency coupled with the a modified MESI protocols in the processors themselves for keeping track of what cache items were valid or not.

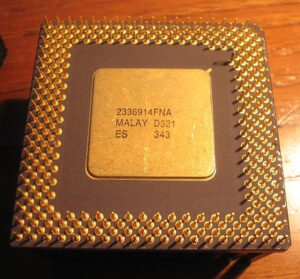

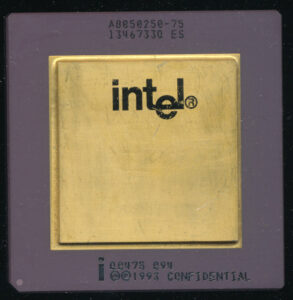

P54CM50-75 Q033 – Early October 1993 Sample – 75MHz modified Socket 5

After the release of the first (P5 Socket 4) Pentiums Intel decided to integrate an APIC onto the CPU core itself. This greatly simplified dual processor setups. Within only a few months of the release of Socket 4, Intel was already working on the P54C Pentium. These were to be on a whole new socket, Socket 5 (much to the annoyance to those who had just dropped some serious coin on a Socket 4 system). The Socket 5 systems, using the Intel Neptune 430NX chipset, would support dual processor systems. To do this Intel designed a separate Pentium Processor core called the P54CM, and originally, a separate, slightly modified socket for it. The secondary socket had a slightly different pin out, and was to run the P54CM processor, OR, could be used as an OverDrive socket, with the Overdrive becoming a second CPU (why both, no one is entirely sure).

| P54CM50-75 Q033 – Mod Socket 5 – Oct 1993 |

Q0475 Nov 1993 – Standard Socket 5 |

|

|

Samples of the P54CM debuted in October of 1993 using the new pinout. Samples from just weeks later had reverted to the standard Socket 5 pinout, clearly someone at Intel decided that yet another socket (and package) design would be uneconomical. The separate core, however, remained.

Early Pentium Print Ad shows the modified Socket.

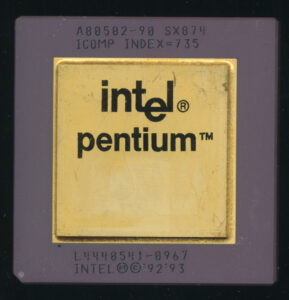

The P54CM core was only produced in a very few specs, SX874 B1 stepping in STD Voltage (3.135V–3.465V) and the SX942 (STD) SX943 (VRE 3.3V–3.465V) and SX944 (MD: faster timings on several pins/3.135V–3.465V) series in the B3 stepping. There were also several ES versions made: Q033 P54CM50-75, Q0475, Q0519 and Q0520 with the B0 stepping and Q0543 with the B1 stepping. These processors, including the production versions, were incredibly rare. Very few companies used them in actual machines. Why? Because a normal (providing it supported dual processing) P55C could be ran just as well. The only real difference in the P54CM core was the DPEN/ output pin was driven low on RESET. On a P54CM this pin is an output that tells the primary processor ‘hey a second processor exists’ while on the standard P54C, DPEN/ is an input.

SX874 – P54CM-B1 (with the FDIV bug) from October 1994

It turns out that the P54C/CM core ALSO has a CPUTYPE pin that can be be set to tell a system that the processor is a secondary processor or a primary (and early Pentium Dual boards had a jumper to do just this.) You didn’t actually NEED a P54CM as the secondary processor. a normal P54C would work just fine. There was even some trickery to allow a system to boot off of a secondary P54CM CPU, not officially supported by Intel, but in systems designed for redundancy, the DPEN/ pin could be overridden and the P54CM used to boot a system (normally the primary CPU would handle all the boot up duties and only enable the secondary CPU once it was ready).

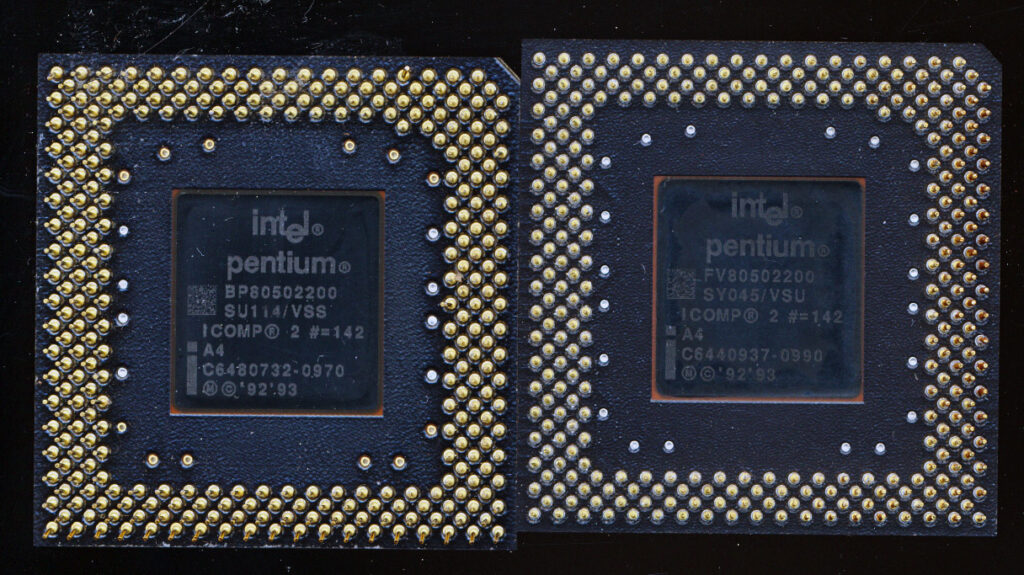

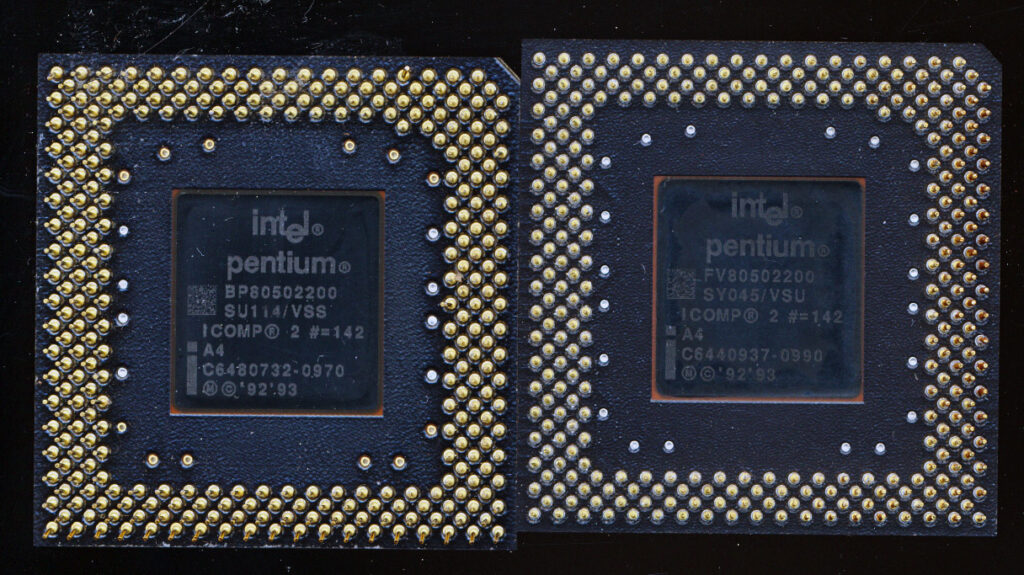

Later Socket 5/7 Pentiums (C0 and later steppings) supported multiprocessing natively with a few exceptions. The SU114/SL25H Pentium 200s did not have a functional APIC so thus were not DP compatible. These were even mismarked by Intel, with the marking ‘VSS’ on the back. That last ‘S’ means they were tested to support UP, DP and MP configurations, when in fact they were not, the code on the back should have been VSU (‘U’ means they were tested for MP, and uniprocessor, but NOT DP, as DP required a working APIC). The SY045 (200) and SY037 (166) were also ‘VSU’ processors, not tested for DP use, likely because of some issue with the APIC.

Mismarked SU114 (VSS) and correctly marked SY045 VSU

Intel Overdrive processors suffer a similar fate, they will not run in the primary socket of a DP system, but will in the secondary socket. This is mostly likely because the DPEN/ is not supported as an input on the Overdrive, so it wouldn’t know a secondary processor exists, a shame really as a dual OverDrive system would be pretty neat.

At he beginning of the P5 era Intel seemed to be all in on DP systems, but with the coming release of the Pentium Pro, they began to use Dual Processing as a way to differentiate their products. DP support was removed in the next Pentium chipset (the FX Triton) only to later return in the HX Triton II. The VX and TX Pentium Chipsets also lacked DP support.

Quite famously later in the 1990s Intel marketed the Pentium II/III with multi-processor support, and sold the Celeron as uniprocessor only. It turned out that the lowly Celeron was quite happy to run in DP configuration, much to the annoyance of Intel, but joy of enthusiasts around the world. Perhaps someone will figure out a way to run Pentium Overdrives in dual processor systems, if there is a will there tends to eventually be a way.