TI TMS7000: The SCAT Microcontroller

The 1980’s brought many 8-bit microcontrollers to the market, such famous designs as the Intel MCS-51, the Zilog Z8, and the Motorola MC680x. There were many others as well, including TI’s entry into the market. After the race into the market with one of the first microcomputers, the 4-bit TMS1000, and the top of the line TMS9900 16-bit processor, TI saw the need to fill in the middle, the 8-bit market. TI didn’t want to make the 7000 series just another 8-bit MCU either, they wanted something different, not so different as to be eccentric, but something to set them apart. They did so with an innovation they called SCAT.

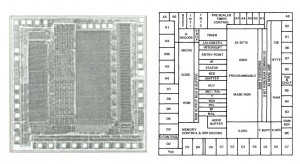

TMS7020 (2K EPROM + 128 bytes RAM) SCAT Layout. Notice the ‘strips’ that form the different sections of the MCU (click to enlarge)

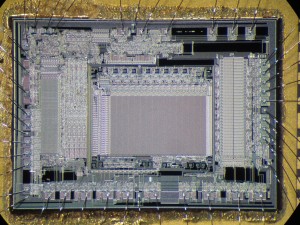

SCAT, Strip Chip Architecture Topology, was TI’s die layout design for the TMS7000. Instead of generating each of the blocks for the chip (SLU, ROM, RAM, etc) making them as small as possible, and then using random logic to tie them all together, they laid them out in strips on the die. The ROM in a strip, the RAM in a strip, and the ALU etc in another. This allowed the sections to be wired up with a minimum of random logic, resulting in a smaller die, that was also easier to test. More importantly it allowed the TMS7000 to be easily expanded. Adding more ROM, or RAM didn’t require redoing the entire layout, it was just added to its respective ‘strip’.

TMS7742 – 4K EPROM with serial + extra timers and 256 bytes of RAM. Notice how the strips just grew, but the layout remains the same

One of the strips was a microcode ROM, it is what held the microcode for the 61 instructions of the TMS7000 architecture. About 75% of these were considered ‘essential’, but the other 25% could be user defined, the TMS7000 was a microprogrammed MCU, custom instruction sets were supported, and even encouraged by TI. Not only could user programs be stored in the user ROM, but if those programs needed custom instructions, that was supported as well. That allowed customers to tailor the 7000 to their needs much easier than the competition. If a programmer found themselves using a set of instruction repetitively, they could program that set into the micrcode, and replace it with a single instruction, resulting in much more dense code. That, coupled with the TMS7000 already good performance made it one of the fasted MCUs of its time, beating the 8051, Z8, and 6801 in most benchmarks.

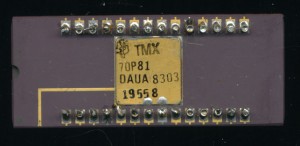

The TMS7000 was released in 1981 on a 5V NMOS process at a clock speed of up to 8MHz. A LMOS (low power NMOS) version was also released known as the TMS70Lxx which used a tenth the power, but ran at only 1MHz. In 1985 a CMOS version was released which was made with the NMOS version into the late 1990’s. The 7000 series was used widely in diverse applications, from early scanning electron microscopes, to anti-lock break systems. This was largely due to the wide variety of parts available, the great development support from TI, and a fairly easy to use architecture. Development versions were available in piggyback packages, where an EPROM sits on top the main chip. The prototyping versions (TMS70P160 and 162) supported standard 2764 and 27128 EPROMs. The TMX77P81 pictured was a prototype for the never released 8K EPROM version (TMS7081). A CMOS version of the 8K EPROM was released as the TMS77C82.