Makings of a Comet: The VAX 11/750

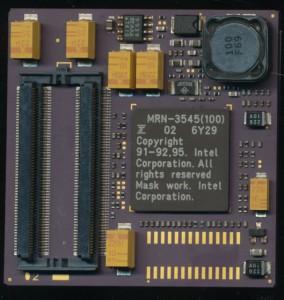

In the mid-1970’s DEC saw the need for a 32-bit successor to the very popular PDP-11. They developed the VAX (Virtual Address eXtension) as its replacement. Its important to realize that VAX was an architecture first, and not designed from the beginning with a particular technological implementation in mind. This varies considerably from the x86 architecture which initially was designed for the 8086 processor, with its specific technology (NMOS, 40 DIP, etc) in mind. VAX was and is implemented (or emulated as DEC often called it) in many ways, on many technologies. The architecture was largely designed to be programmer centric, writing software for VAX was mean to be rather independent of what it ran on (very much like what x86 has become today).

The first implementation was the VAX 11/780 Star, released in 1977, which was implemented in TTL, and clocked at 5MHz. TTL allowed for higher performance, but at the expense of greater board real estate as well as somewhat less reliability (more IC’s means more failure points). It also cost more, to purchase, to run, and to cool.

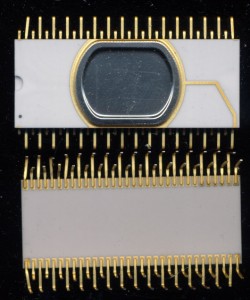

DEC followed the Star with the 11/750 Comet in 1980. This was a value version of the Star. It ran at only 3.12MHz (320ns cycle time) but introduced some new technology. Part of the ‘value’ was a much smaller footprint. The TTL had been replaced by bi-polar gate arrays. Over 90% of the VAX architecture was implemented in the gate arrays, and there was a lot of them, 95 in a complete system with the floating point accelerator (28 arrays). The CPU and Memory controller used 55 while the Massbus (I/O) used an additional 12 gate arrays. The 95 gate arrays though replaced hundreds of discrete TTL chips. And as a further simplification they were all the same gate array.

Posted in:

CPU of the Day