Microprocessor Museum of CPU History for Intel CPUs, AMD Processor History, Cyrix Microprocessors, Microcontrollers and more.

Total CPU's: 2342

Total Manufacturers: 32

Total EPROM's: 23

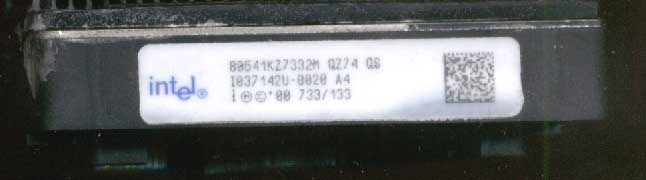

Itanium > Intel80541KZ7332M-QZ74-QS

|

|

|

Modified: May 8, 2005, 12:40 am

|