CPU of the Day: DEC LSI-11 Chipset

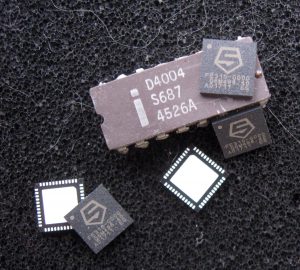

Back in 2014 we discussed the Western Digital WD/9000 Pascal Microcomputer system. Today we’ll look at the LSI-11 chip set, the basis of the Pascal. Back in 1974 DEC (Digital Equipment Corporation) contracted Western Digital to design and build a 16-bit chipset to emulate the Bipolar PDP-11/05 Minicomputer. Western Digital was paid $6.3 million for the work, and would be allowed to market and sell the resulting chipset themselves, as well as grant license to it to others (including DEC).

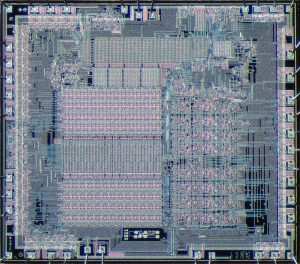

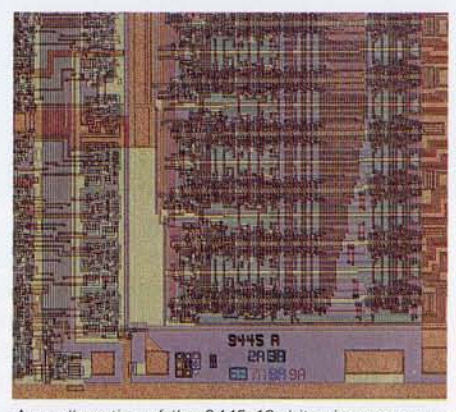

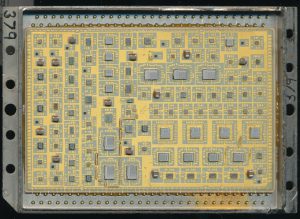

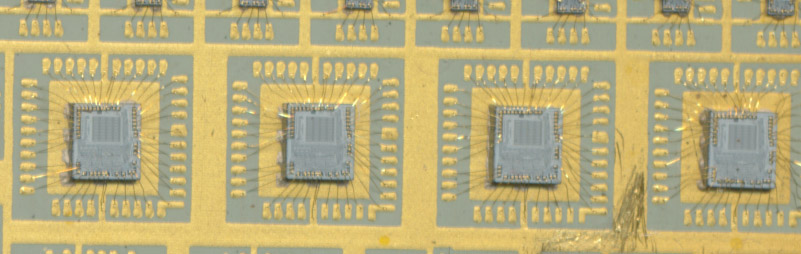

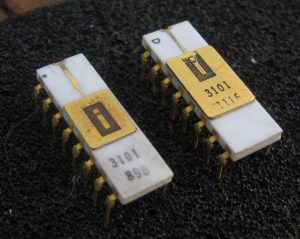

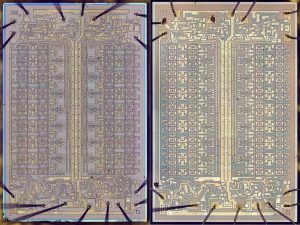

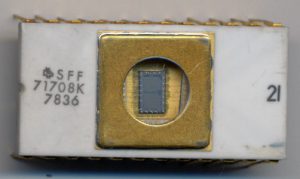

The LSI-11 was to be a 16-bit chipset, but was based around a 8-bit Data chips (the 1611). The 1611 has an 8-bit ALU , 26 8-bit registers and a microinstruction register. This is controlled by the 1621 control chip, which interprets macroinstructions from handles all the timing, as well as interrupts. The 1621 control chip is what allows the 8-bit 1611 to be used as a 16-bit processor. The chips are connected by an 18-bit microinstruction bus, and a 16-bit address/data bus handles access to the rest of the system (memory/I/O). Each microm is a 512 Word by 22-bit ROM, which can hold 80 instructions. It is these MICROMs that allow the WD MCP1600 to function as a PDP-11/05. The instructions in the the MICROMs (2 are required for the LSI-11) emulate the PDP-11 instructions.

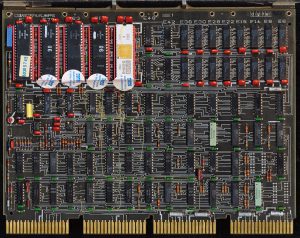

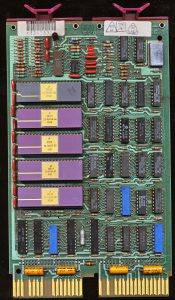

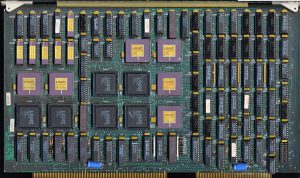

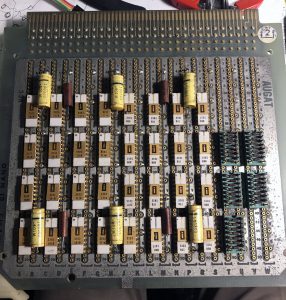

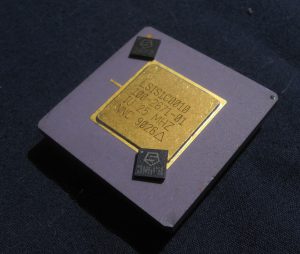

First production of the LSI-11 chipset began in March of 1975 with shipments commencing that year. The PDP-11/03 based on this chipset was released later that year. The KD-11 M7264 board formed the hear of the 11/03 (as well as other DEC systems). In typical DEC fashion it came in many flavors with different amounts of memory, as well as different instruction support. This was completely due to the design of the LSI-11 chipset and its MICROMs . The basic LSI-11 needs 2 MICROMs to handle the basic PDP-11 instructions, the chipset however supported 4. This means that more instructions could be added. One of the most common and useful additions was the EIS/FIS (Extended Instruction Set/Floating Point Instruction Set) microm. This added 8 more instructions including MUL, DIV, FADD, FSUB, FMUL, FDIV and 2 register shifts (ASH, ASHC). Adding the EIS/FIS chip to a standard KD-11-F board turned it into a KD-11-L (like the one pictured).

There were other MICROMs available as well. This included a set of 2 for support of DIBOL (Digital Business Oriented Language), a DEC language similar to COBOL. Since the DIBOL chipset needed 2 chips a system could support DIBOL, OR EIS/FIS but not both. MICROMs were revised as bugs were found, or faster ways of handing an instruction were made. MICROMs revisions could also be made to support different PCB revisions. In some ways they played the part of firmware to the PCB, as well as the instruction set for the processor. In this way many MICROMs are specific to PCB etch revisions and other revisions of the system outside of the processor itself. Matching the correct MICROMs, as well as Control and Data chips to the correct board is a bt of a task, and take several dozen pages of the LSI-11 maintenance manual.

Here are a few part #s to help sort things out

| Data Chip DEC 1611 |

Control Chip DEC 2007C |

MICROMs MICROM 1 3010D/A MICROM 2 3007D EIS/FIS 3015D |

Notes |

| 21-11549-01 | 23-008B5-00 | STD INST 1 | |

| 21-15579-00 (1611H) | 23-003C4-00 | 23-007B5-00 | STD INST 2 |

| 21-16890-00 (1611H) | 23-002C4-00 | 23-003B5-00 | EIS/FIS |

| 23-001C3 CP1621B14 | 23-009B5-00 | EIS/FIS | |

| 23-001C2-01 CP1621B451 | 23-001B5-00 CP1631B103 | STD INST 1 | |

| 23-002B5 CP1631B073 | STD INST 2 | ||

| 23-091A5-01 CP1631B153 | EIS/FIS | ||

| 23-004B5 | DIBOL 1 | ||

| 23-005B5 | DIBOL 2 | ||

| 23-008A5-01 CP1631B-10 | STD INST 1 | ||

| 23-007A5-01 CP1631B-07 | STD INST 2 |

There are more to be found as DEC and Western Digital made many versions. In early 1976 Western Digital licensed the MCP1600 chipset design to National Semiconductor, in exchange for some RAM technology licensing. It is unclear if National actually made any of the MCP1600 chipset. By 1977 DEC had started to produce the LSI-11 chip itself while continuing to source parts from Western DIgital as well. It is common to see LSI-11 boards with DEC and WD chips mixed well into 1982.

The popularity of the PDP-11 in the 1970’s resulted in many customers for the LSI-11 based PDP’s, and their use continued well into the 1990’s with many systems continuing to be used today. As with many such systems, they found use in industrial control and automation, where they continue to work.