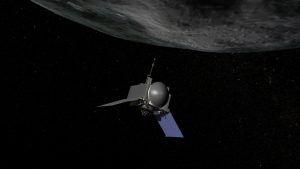

OSIRIS-REx: Bringing Back Some Bennu

The Apollo Group carbonaceous asteroid Bennu is a potential Earth impactor, with a 0.037% likelihood of hitting earth somewhere between 2169 and 2199. Bennu is thought to be made of materials left over from the very early beginnings of our solar system, making researching them a very tantalizing proposition. Rather than wait for the small chance of Bennu delivering a sample to Earth in 150 years the thoughtful folks at NASA decided to just go fetch a bit of Bennu. Thus is the mission of OSIRIS-REx which was launched a few days ago (Sept 8, 2016) aboard an Atlas V 441 as an $850 Million New Frontiers mission.

Somewhat surprisingly there is scant details about the computer systems that are driving this mission to Bennu. OSIRIS-REx is based on the design of the Mars Reconnaissance Orbiter (MRO), MAVEN and Juno, and thus is based on the now ubiquitous BAE RAD750 PowerPC processor running the redundant A/B side C&DH computers. This is the main ‘brain’ of the Lockheed Martin built spacecraft. Of course the dual RAD750s are far from the only processors on the spacecraft, with communications, attitude control, and instrumentation having their own (at this point unfortunately unknown) processors.

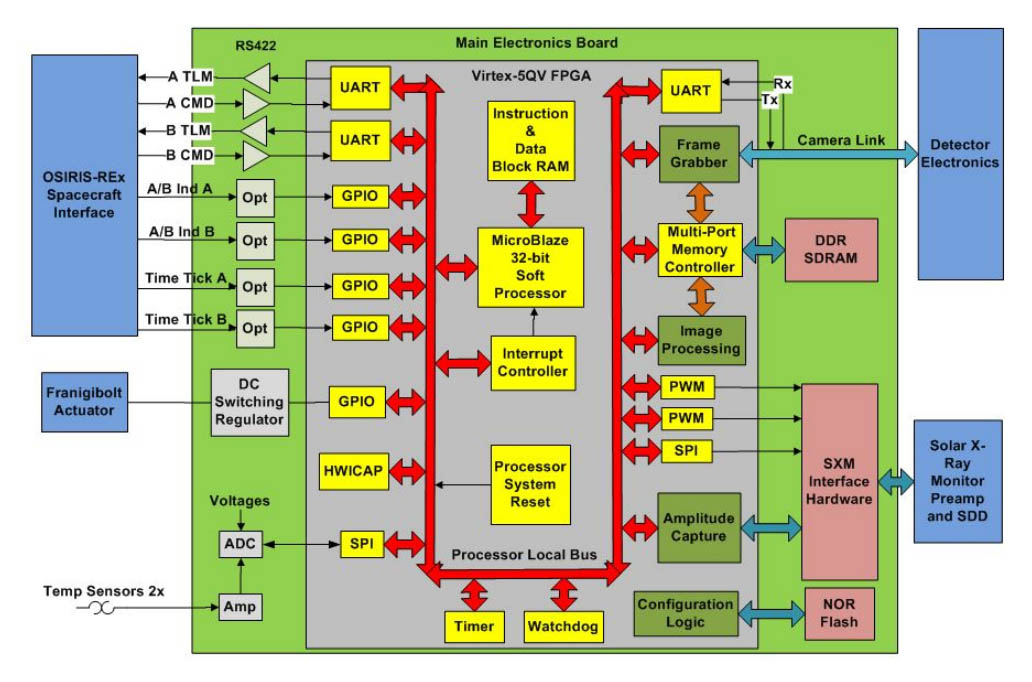

REXIS Electronics: Virtex 5QV – Yellow Blocks are Off the Shelf IP, Green Blocks are custom by the REXIS Team. Powered by a Microblaze SoftCore.

One instrument in particular we do know a fair amount about though. Regolith X-ray Imaging Spectrometer (REXIS) is a student project from Harvard and MIT. REXIS maps the asteroid by using the Sun as an X-ray source to illuminate Bennu, which absorbs these X-rays and fluoresces its own X-rays based on the chemical composition of the asteroid surface. In addition REXIS also includes the SXM, to monitor the Sun’s X-Rays providing context to what REXIS is detecting as it maps Bennu. REXIS is based on a Xilinx Virtex-5QV Rad-Hard FPGA. This allows for a mix of off the shelf IP blocks, and custom logic as well. The 5QV is a CMOS 65nm part designed for use in space. Its process, and logic design are built such as to minimize any Single Event Upsets (SEU), and other radiation induced errors. It is not simply a higher tested version of a commercial part, but an entirely different device. Implemented on this FPGA is a 32-bit RISC softcore processor known as Microblaze. The Microblaze has ECC caches implemented in the BRAM (Block RAM) of the FPGA itself and runs at 100MHz.

It will take OSIRIS-REx 7 years to get to Bennu, sample its surface, and return its sample to Earth. By the time it gets back, the RAD750 powering it may not be so ubiquitous, NASA is working on determining what best to replace the RAD750 with in future designs. Currently several possibilities are being evaluated, including a QuadCore PowerPC by BAE, a QuadCore SPARC (Leon4FT), and a multi-core processor based on the Tilera architecture. As with consumer electronics, multi-core processors can provide similar benefits in space of hogher performance and more flexible power budgeting all with the added benefit (when design for such) of increased fault tolerance.