Microchip PIC’s up Atmel

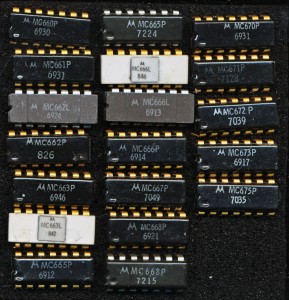

Yesterday Microchip, makers of the PIC line of microcontrollers, announced they were buying Atmel, for a cool $3.56 Billion. This isn’t entirely surprising considering the ongoing consolidation in the industry, It was only last year that Dialog attempted to purchase Atmel, and before that ON Semiconductor and Microchip. In December of 2015 NXP and Freescale (formerly Motorola Semiconductors) merged, creating one of the largest microelectronics companies. These mergers do create an interesting result, product mixes that were formerly competitors, end up being marketed side by side. In the case of NXP and Freescale, NXP marketed many MCS-51 microcontrollers in their 8/16-bit lines, while Freescale of course sold many versions of MC6800 based MCU’s. These two rivalries have existed since the early 1980’s and likely will continue. Perhaps the biggest rivalry in MCU though is between Atmel and Microchip.

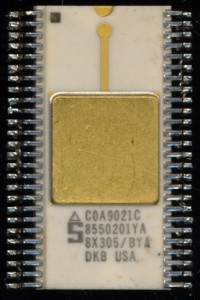

Microchip was spun off of General Instrument in 1987, but the PIC architecture dates back to 1976, and is still being made in nearly the same form (PIC16C55). Atmel was started in 1984, first making EPROMs, and then MCS-51 microcontrollers, one of the very first companies to make an 8051 with on die flash memory. In a bit of a twist of fate, when Atmel started, it was a fabless company, it contracted with several companies to make its EPROMs, including Sanyo, and General Instruments, which as mentioned above, became Microchip. Atmel also makes APRC processors, and for a time made Motorola products as well (Atmel has a very convoluted history, for more info on this read here and here )

Today the PIC line continues to be popular, with devices for the low end, such as the PIC10/12 all the way to the MIPS based PIC24 on the upper end. Atmel continues to make 8051 MCUs, but also makes the 8 and 32-bit AVR line, perhaps best known today for its use in Arduino boards. They also make MCU’s based on the ARM core, a competitor to MIPS, and Atmel’s own AVR32.

Likely to the consternation to many fans of either company, this merger does make sense, more so than ON or Dialog buying Atmel. While Microchip and Atmel both compete in the same markets, they do so with different architectures. Product lines are unlikely to change, and overhead saving should free up $$ both for stockholders (yawn) and engineering teams alike. No word has been giving yet on wether Microchip intends to keep the Atmel branding, but perhaps they should, as an AVR MCU with a Microchip logo on it may just prove to be too much for some.