Western Digital and the COP

In the 1970’s second sourcing was the name of the game. Processors that had no additional source available often struggled in the market. Designers wanted to ensure that if they invested in designing a product around a chip, that chip would remain available if the original manufacturer of it had issues. It also helped drive down pricing, as often second sources could compete on price with the original manufacturer.

By the 1980’s second sourcing had begun to end. It did still happen, but began to take the form of fabless semiconductor companies today. A company would create a design and then license its manufacturing to other companies.

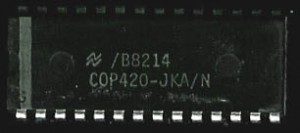

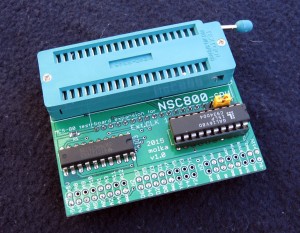

National Semiconductor was a popular second source for many processors of the 1970’s, notably Intel’s 8080, MCS-48 microcontrollers and AMD’s 2901. For their own designs, they rarely second sourced to anyone. Such designs as the PACE, SC/MP, original COPS and NSC800 were exclusive to National. In the 1980’s they did have TI make a very limited amount of 32k processors, likely due to some of the reliability problems National was having in making them themselves early on. So it is a bit surprising that they licensed the COPS II to Western Digital in the early 1980’s.

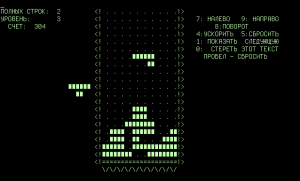

The COPS II (later just called COPS) was the 2nd generation COPS 4-bit microcomputer made by National. It was a NMOS design, designed for basic control oriented applications to replace the PMOS COPs from 1976. Western Digital already had the 4-bit CR1872 PMOS processor, as well as the CP1611 16-bit design. Perhaps WD saw the COPS as a filler between those. It certainly didn’t replace the CR1872, as that design continued to be marketed up until the mid-1980’s.

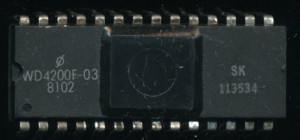

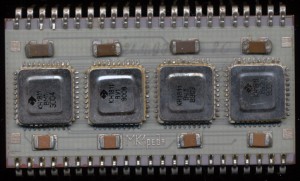

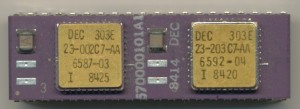

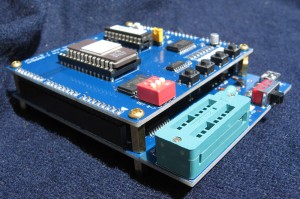

Western Digital made the WD4200 and WD4210 as copies of the National COP420 and COP421. Also made was a WD4020 copy of the COP402 (the ROMLESS version used for dev work). The WD4200 and WD4210 are nearly identical to each other. The 4200 comes in a 28-pin package while the 4210 came in a 24-pin package. WD (and National) called this a bond-out option. The die is the same in both, the 4210 merely has one 4-bit input port left unconnected (IN0-IN3). A 24-pin package was enough less expensive than a 28-pin package to make this a viable sales option. Using a bulk NMOS process the die itself was a fairly insignificant cost compared to packaging and testing. The smaller package also was useful for smaller board designs. The practice continues today with features on processors and MCU’s disabled/enabled to expand a product line and/or make use of die’s with defects.

WD continued to produce the COP line until at least 1983. Western Digital was moving its focus to the storage market, and away from te general purpose processor/microcomputer market. This brought an end to the WD4200 as well as WD’s other processors. Today WD is known for hard drives, and remembered for their disk controllers. that they second sourced a 4-bit design from National has faded to the annuls of history.