Western Digital WD/9000 Pascal MicroEngine

Fully 10 years before Western Digital released their first hard drive, they made processors, calculator chips, Floppy Disk controllers and a host of other IC’s. Western Digital began in 1970 making primarily calculator chips. In 1976 they announced the multi-chip MCP-1600 processor. This was an implementation of the PDP-11 minicomputer in silicon. It consisted of a CP1611 Register/ALU chip, a CP1621 control chip and either 2 or 4 CP1631 512x 22bit MICROMs that contained the microcode implementation of the PDP-11 architecture. Physically this was an 8-bit design, but clever microcode programming allowed it to function as a 16-bit processor. Use of microcode allowed it to also implement floating point support, a very new concept in hardware in 1976. The MCP-1600 was used in DECs LSI-11 microcomputer among others.

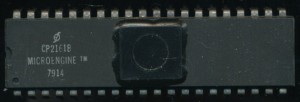

Having the microcode separate from the ALU/Control didn’t help with board layout or cost, but it did provide a very flexible platform to implement other architectures on. In the late 1970s UCSD (University of California in San Diego) was working on a project, led by Kenneth Bowles, to make a portable version of the Pascal programming language, a version that could run on multiple hardware platforms, very similar to how Java has become today. The code was compiled to a ‘p-code’ or pseudo code that could them be executed by a virtual machine onto whatever hardware. Typically this virtual machine would be implemented in software, however the design of the MCP-1600 was such that it could be implemented in hardware, or rather microcode. Thus in 1978, the WDC MICROENGINE was born. This was to be a 5 chip set (original documentation states 4, but it ended up being 5) that consisted of the CP2151 Data chip (if you have a CP2151 you would like to donate, let us know) , the CP2161 Control chip, and 3 512 x 22 bit MICROMs which contained the microcode to directly execute UCSD Pascal on the data chip. The CP2151 was no different from the CP1611 of the MCP-1600 chipset and could be interchanged.