DEC M7260 KD11-A CPU: The PDP-11 Goes MSI

Back in 1972 DEC released the ‘budget’ PDP-11/05 16-bit computer. The original PDP-11/20 had been released 3 years before and its CPU (the KA11) was based on simple TTL, its ALU could perform adds and that was all, which meant its designers had to get creative in implementing the instruction set. By 1972 however things had changed, there still was no 16-bit processors available but there was now single chip 4-bit ALU’s. The ALU was the famous 74181 and formed the heart of the KD11-A, DEC’s 4th processor design (the ‘third’ was the KB11-A which was similar but based on the faster 74S181 and used in the PDP-11/45 and released at the same time) .

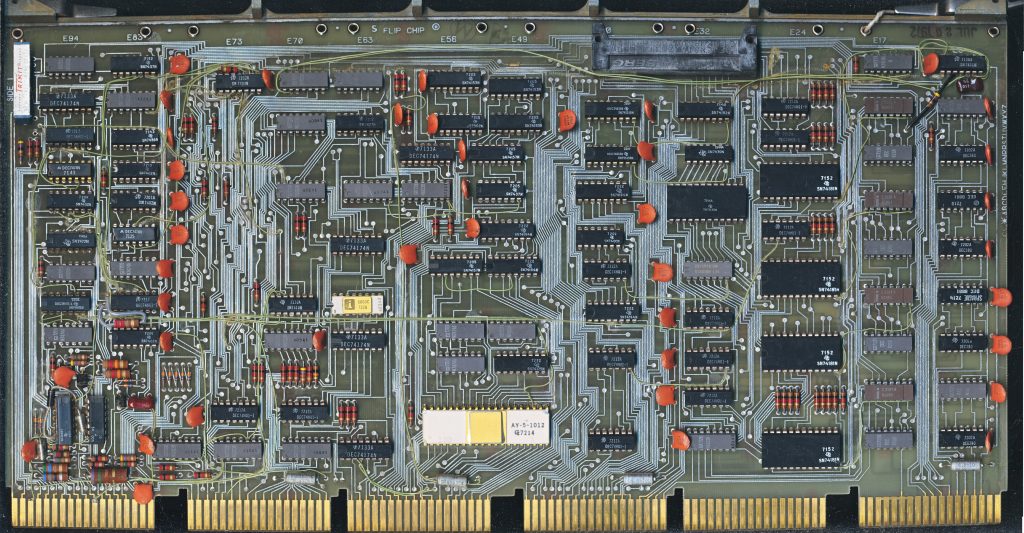

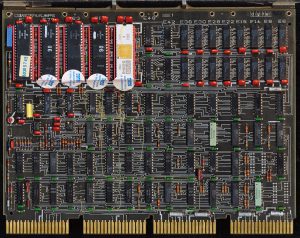

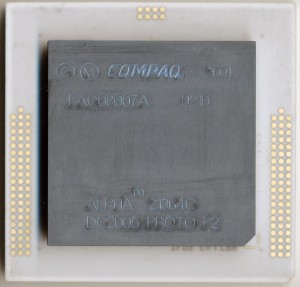

The KD11-A consisted of a pair of boards, the M7260 Data Path Module and the M7261 Control Logic and Microprogram Module. All the processor functional components are contained on these modules. The M7260 Data Path Module contains: data path logic, processor status word logic, auxiliary arithmetic logic unit control, instruction register and decoding logic, and serial communications line interface. The M7261 Control Logic and Microprogram Module contains: internal address detecting logic, stack control logic, Unibus control logic, priority arbitration logic, Unibus drivers and receivers, microbranch logic, microprogram counter, control store logic, power fail logic, line clock, and processor clock. The M7260 was he brain, and the M7261 told it what to do, containing the microcode to implement the PDP-11 instruction set. This was the first version (with the 11/45) of the PDP-11 that was microcoded.

The KD11-A ran off a single 150ns clock resulting in a raw clock speed of 6.67MHz, however performance was limited by memory access speed. The PDP-11/05 supported up to 32K Words (64KB) of core memory and this memory could only run at a 980ns cycle time. This limited the 11/05 performance to around 1MHz. This was still quite good for 1972!.

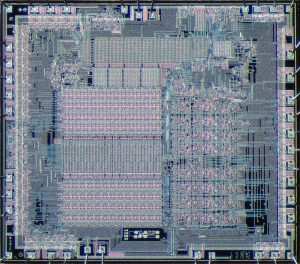

The 74181 was capable of running at 42MHz (and 90MHz for the 74S181 Schottky TTL versions) but in a set of 4 this drops to about 27MHz (with the carry generator taking some time). Speed, however, is usually limited by other things rather then the ALU itself. The 74181 ALU contains the equivalent of 62 logic gates (170 transistors) and can perform 16 different arithmetic and logic functions on a pair of 4-bit inputs. Ken Shirriff did an excellent die level analysis of a ‘181 thats worth reading. It includes pretty pictures even.

This particular KD11-A board is one of the very first made. It is dated July 20th 1972, a month after the initial release of the 11/05. The big white chip is a General Instruments AY-5-1012 UART. To its right you can see thr 4 74181 ALUs. Each is 4-bit and together they form a complete 16-bit ALU for the CPU. A 74150 Multiplexer helps determine what data goes where. The 74182 is the Look ahead carry generator for the ‘181’s. Most of the rest of the chips on the board are ROMs and supporting logic. There is also 4 Intel C3101A 35ns SRAM chips, these are 16×4 SRAMs used as scratch pad memories and only were used in the very first version of the CPU (later versions replaced them with cheaper 7489 TTL versions). The Scratch Pad Memory is what forms the registers for the CPU. There are 16 16-bit registers with the the first 6, R0-R5 being general purpose registers and the rest special purpose such as the Program Counter, Interrupt Vector, etc.

Another interesting point on this board is the very large amount of green wires running on the board. These are called ECO wires, which are ‘Engineering Change Order’ wires, and are placed, by hand, after the board is made to correct faults in the board layout. The goal is to not have these as they are expensive and delicate and can result in failures down the road, so further revisions of the board would have these fixed/implemented in the PCB. You do not see these much at all any more as modern design/testing tools virtually eliminate the possibility of a faulty PCB layout making it into production.

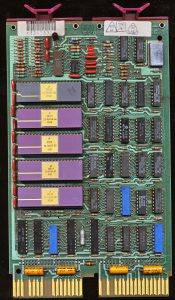

When it was released the ~1MHz 11/05 cost $25,000, which in 2020 US Dollars is around $154,000. THe PDP-11 series ended up being one of the most popular minicomputers, selling over 600,000 units over the years. Later versions like the LSI-11 series moved the entire CPU to a single LSI chip, adding Extended Instructions, Floating Point Instructions, faster memories and other performance enhancements well into the 1980’s. It was also widely comied, and enhanced in the Soviet Union and Russia. It was on a Soviet PDP-11 clone that Tetris was developed, a game we are all rather familiar with.

Its amazing to see where computers have come in the span of but a few decades. but these important parts of history continue to be used. Perhaps not the 11/05, but there are many PDP-11 systems still working away, typically inindustrial environments, ironically helping produce things likely far more advanced then themselves.

Posted in:

CPU of the Day