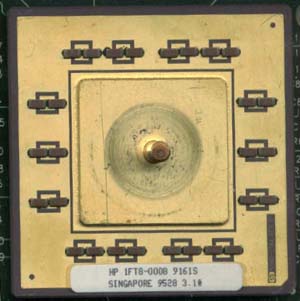

PA-7000 (PCX-S)

Overview

This really was a multichip CPU and was used in Nova severs. It is the first ose of PA 1.1

Details

| PA-RISC Version |

1.1a (32 bit) |

| FPU |

External |

| Process |

1.0u 2-Layer CMOS |

| Die Size |

14.2 x 14.2 mm2 die |

| Introduced |

1987? |

| |

|

| |

|

|

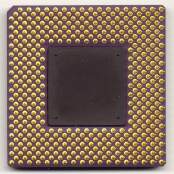

PA-7100/PA-7150 (PCX-T) (Thunderbird)

Overview

The 7100 is a true superscalar CPU, with ALU units as well as an onboard FPU.

The 7150 is an enhanced 7100 with a higher clock speed.

Details

| PA-RISC Version |

1.1b (32 bit) |

| FPU |

Single FPU |

| Process |

0.8u 3-Layer CMOS |

| Die Size |

14.0 x 14.0 mm2 die |

| Introduced |

1992 |

| |

|

| |

|

|

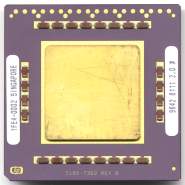

PA-7100LC (PCX-L) (Hummingbird)

Overview

This is a low cost CPU meant to integrate many of the support chips (FPU MPU etc) on the same chip

Details

| PA-RISC Version |

1.1c (32 bit) |

| FPU |

Single FPU |

| Process |

0.75u 3-Layer CMOS |

| Die Size |

14.2 x 14.2 mm2 die |

| Introduced |

1994 |

| |

|

| |

|

|

PA-7200 (PCX-T')

(Thunderbird')

Overview

The PA-7200 is a die shrunk and frequency enhanced PA-7100, with a few extra enhancements to bring it to PA 1.1d revision level. It still requires off chip cache running at core speed. (140MHz)

Details

| PA-RISC Version |

1.1d (32 bit) |

| FPU |

Single FPU |

| Process |

0.55u 3-Layer CMOS |

| Die Size |

14.0 x 15.0 mm2 die |

| Introduced |

1995 |

| |

|

| |

|

|

PA-7300LC (PCX-L2) (Velociraptor)

Overview

The PA-7300LC is an enhanced 7100LC with ondie L1 cache (courtesy of the process shrink)

Details

| PA-RISC Version |

1.1e (32 bit) |

| FPU |

Single FPU |

| Process |

0.50u 4-Layer CMOS |

| Die Size |

15.3 x 17.0 mm2 die |

| Introduced |

1996 |

| |

|

| |

|

|

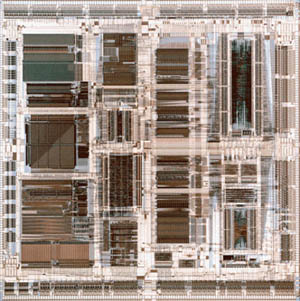

PA-8000 (PCX-U) (Onyx)

Overview

The PA-8000 is the first chip to implement the 64-bit PA-RISC

2.0 architecture. It again, in HP tradition, has large off de primary caches.

Details

| PA-RISC Version |

2.0 (64 bit) |

| FPU |

Quadruple FPU's |

| Process |

0.50u 5-Layer CMOS |

| Die Size |

17.7 x 19.6 mm2 die |

| Introduced |

1996 |

| |

|

| |

|

|

PA-8200 (PCX-U+) (Vulcan)

Overview

Nothing more then a PA-8000 with a few sdesign fixes implemented.

Details

| PA-RISC Version |

2.0 (64 bit) |

| FPU |

Quadruple FPU's |

| Process |

0.50u 5-Layer CMOS |

| Die Size |

17.7 x 19.6 mm2 die |

| Introduced |

1997 |

| |

|

| |

|

|

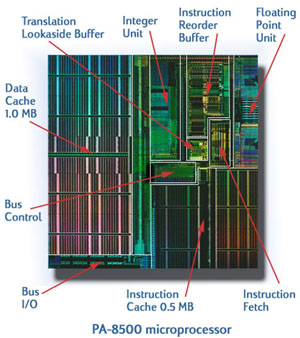

PA-8500 (PCX-W)

(Vulcan)

Overview

The PA-8500 is a direct decendent of the 8000. It features a higher clock speed and a MASSIVE 1.5MB on die L1 cache (most other chips of the time were running 32kB L1 caches)

Details

| PA-RISC Version |

2.0 (64 bit) |

| FPU |

Quadruple FPU's |

| Process |

0.25u 5-Layer CMOS |

| Die Size |

21.3 x 22.0 mm2 die |

| Introduced |

1998 |

| |

|

| |

|

|

PA-8600 (PCX-W+) (Landshark)

Overview

A slightly enhanced PA-8500 made to work on a new fab process. Very few changes to the deisgn itself.

Details

| PA-RISC Version |

2.0 (64 bit) |

| FPU |

Quadruple FPU's |

| Process |

0.25u 5-Layer CMOS |

| Die Size |

21.3 x 22.0 mm2 die |

| Introduced |

2000 |

| |

|

| |

|

|

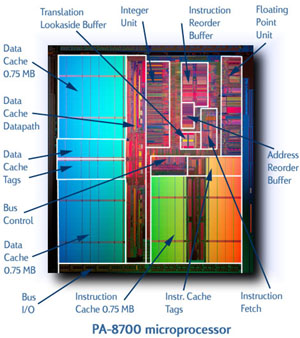

PA-8700 (PCX-W2) (Piranha)

Overview

The PA-8700 is again a enhanced and clock speed increased 8500 The PA-8700 was manufactured

by IBM, in contrast to the PA-8500 and PA-8600, which were fabbed

by Intel, since HP stopped upgrading its fabs long ago. HP still makaes custom chips in its old fabs)

Details

| PA-RISC Version |

2.0 (64 bit) |

| FPU |

Quadruple FPU's |

| Process |

0.18u 7-Layer CMOS SOI |

| Die Size |

16.0 x 19.0 mm2 die |

| Introduced |

2001 |

| |

|

| |

|

|

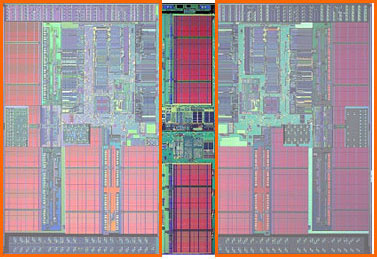

PA-8800 (PCX-??) (Mako)

Overview

The PA-8800, codenamed Mako, features 2 independent microprocessors on a single die. Thus each "chip" forms a 2-way SMP set. Each processor on the 8800 has a 1.5 MB L1 cache, but HP is leaving behind its L1-only design custom by including 32 MB of L2 cache using separate chips. The Runway bus has been replaced by the 6.4 GB/s Itanium2 bus, allowing greater bandwidth and the use of otherwise very similar server designs for both PA-RISC and Itanium.

Details

| PA-RISC Version |

2.0 (64 bit) |

| FPU |

Quadruple FPU's |

| Process |

0.13u 7-Layer CMOS SOI Copper |

| Die Size |

?? |

| Introduced |

2003 |

| |

|

| |

|

|

PA-8900 (PCX-??)

Overview

The PA-8900 is similar to the 8800, but features a faster 64 MB shared L2 and slight core improvements such as better error detection and correction on caches. The cahce has also been brought closer to the cores, which helps reduce latenecy. It is not a die shrink of the 8800, as was earlier rumored. It is the last in the PA-RISC line. THe PA-8900 will be the last PA-RISC CPU and is used in the HP 9000 server line.

Details

| PA-RISC Version |

2.0 (64 bit) |

| FPU |

Quadruple FPU's |

| Process |

0.13u 7-Layer CMOS SOI |

| Die Size |

?? |

| Introduced |

2005 |

| |

|

| |

|

|

Hitachi PA/50

Overview

The PA/50 were PA-RISC version 1.1 compatible PA-RISC CPUs designed

and manufactured by Hitachi. Two designs were developed: the ' M'

and ' L'. The ' L' being a lower cost lowe voltage (3.3V) embedded version.. They were

meant as personal workstation or high-end embedded controllers.

Hitachi also integrates L1 cache onto the die

Details

| PA-RISC Version |

1.1 (32 bit) |

| FPU |

SIngle Pipelined FPU |

| Process |

0.6u 3-Layer CMOS |

| Die Size |

11.5 x 12.0 mm2 die |

| Introduced |

1993 |

| |

|

| |

|

|

Hitachi HARP-1

Overview

The HARP-1 also was a PA-RISC version 1.1 compatible CPU from

Hitachi; It was a enhanced PA/50L and also ran at 3.3V

Details

| PA-RISC Version |

1.1 (32 bit) |

| FPU |

SIngle Pipelined FPU |

| Process |

0.6u 3+1-Layer CMOS (Al + Tungsten) |

| Die Size |

16.2 x 16.5 mm2 die |

| Introduced |

1994 |

| |

|

| |

|

|